# Pulsed-Load Synchronous Regulator with Bypass Mode for GSM PA Supply, TINYBOOST®, 2.5 MHz, 2.0 A

## **FAN48632**

## Description

The FAN48632 allows systems to take advantage of new battery chemistries that can supply significant energy when the battery voltage is lower than the required voltage for system power ICs. By combining built–in power transistors, synchronous rectification, and low supply current; this IC provides a compact solution for systems using advanced Li–Ion battery chemistries.

The FAN48632 is a boost regulator designed to provide a minimum output voltage ( $V_{OUT(MIN)}$ ) from a single–cell Li–Ion battery, even when the battery voltage is below system minimum. In boost mode, output voltage regulation is guaranteed to a maximum load current of 1.5 A continuous and 2.0 A pulsed. Quiescent current in Shutdown Mode is less than 3  $\mu$ A, which maximizes battery life. The regulator transitions smoothly between Bypass and normal Boost Mode. The device can be forced into Bypass Mode to reduce quiescent current.

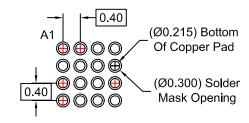

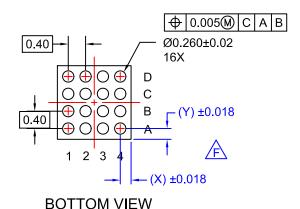

The FAN48632 is available in a 16-bump, 0.4 mm pitch, Wafer-Level Chip-Scale Package (WLCSP).

## **Features**

- Few External Components: 0.47 μH Inductor and 0603 Case Size Input and Output Capacitors

- Input Voltage Range: 2.35 V to 5.5 V

- Fixed Output Voltage: 3.3 V to 3.5 V

- Maximum Continuous Load Current of: 1.5 A at V<sub>IN</sub> of 2.6 V

- Maximum Pulsed Load Current of: 2.0 A for GSM 217 Hz Repetition Rate, boosting V<sub>OUT</sub> to 3.3 V or 3.5 V

- Up to 96% Efficient

- True Bypass Operation when V<sub>IN</sub> > Target V<sub>OUT</sub>

- Internal Synchronous Rectifier

- Soft-Start with True Load Disconnect

- Forced Bypass Mode

- V<sub>SEL</sub> Control to Optimize Target V<sub>OUT</sub>

- Short-Circuit Protection

- Low Operating Quiescent Current

- 16–Bump, 0.4 mm Pitch WLCSP

- These Devices are Pb–Free, Halogen Free/BFR Free and are RoHS Compliant

#### **Applications**

- Boost for Low-Voltage Li-ion Batteries, Brownout Prevention, Supply GSM RF PA

- Cell Phones, Smart Phones, Tablets

## ON Semiconductor®

www.onsemi.com

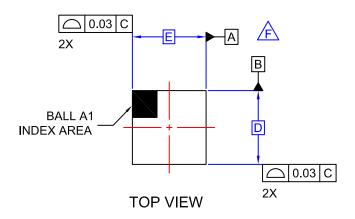

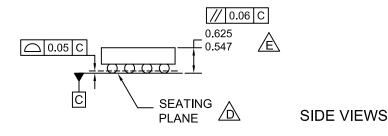

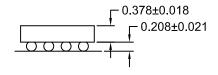

WLCSP16 1.78x1.78x0.586 CASE 567SY

#### MARKING DIAGRAM

12 = Alphanumeric Device Marking

KK = Lot Run Code

X = Alphabetical Year CodeY = 2-weeks Date CodeZ = Assembly Plant Code

## ORDERING INFORMATION

See detailed ordering and shipping information on page 2 of this data sheet.

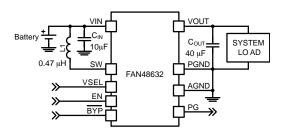

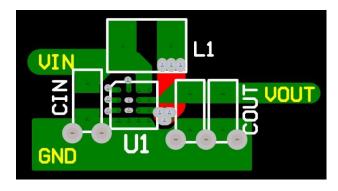

Figure 1. Typical Application

**Table 1. ORDERING INFORMATION**

| Part Number                | Output Voltage<br>V <sub>SELO</sub> /V <sub>SEL1</sub> | Soft –<br>Start | Forced<br>Bypass   | Operating<br>Temperature    | Package                                           | Shipping <sup>†</sup> |

|----------------------------|--------------------------------------------------------|-----------------|--------------------|-----------------------------|---------------------------------------------------|-----------------------|

| FAN48632UC33X              | 3.30 / 3.49                                            | FAST            | Low I <sub>Q</sub> | –40 to 85°C                 | 16–Ball, 4x4 Array, 0.4 mm<br>Pitch, 250 μm Ball, | 3000 / Tape &<br>Reel |

| FAN48632BUC33X<br>(Note 1) | 3.30 / 3.49                                            | FAST            | Low I <sub>Q</sub> | Low I <sub>Q</sub> Wafer–Le | Wafer–Level Chip–Scale<br>Package (WLCSP)         | Neel                  |

| FAN48632UC35X              | 3.50 / 3.70                                            | FAST            | Low I <sub>Q</sub> |                             |                                                   |                       |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

1. The FAN48632BUC33X includes backside lamination.

## **TYPICAL APPLICATION**

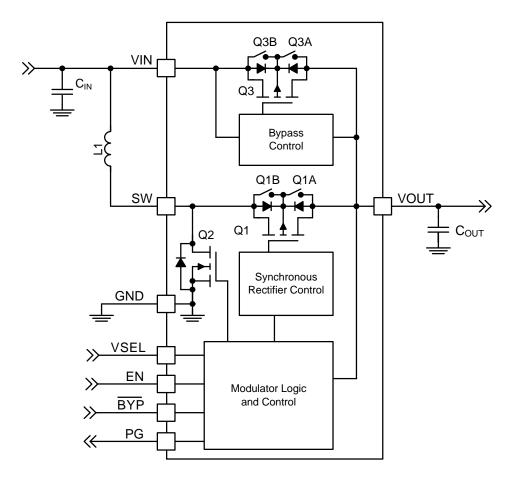

Figure 2. Block Diagram

**Table 2. RECOMMENDED COMPONENTS**

| Component        | Description                                                     | Vendor                         | Parameter      | Тур. | Unit |

|------------------|-----------------------------------------------------------------|--------------------------------|----------------|------|------|

| L <sub>1</sub>   | 0.47 μΗ, 30%                                                    | Toko: DFE201612C<br>DFR201612C | L              | 0.47 | μН   |

|                  |                                                                 | Cyntec: PIFE20161B             | DCR (Series R) | 40   | mΩ   |

| C <sub>IN</sub>  | 10 μF, 10%, 10 V, X5R, 0603                                     | TDK: C1608X5R1A106K            | С              | 10   | μF   |

| C <sub>OUT</sub> | $2 \times 22 \mu F$ , $20\%$ , $6.3 \text{ V}$ , $X5R$ , $0603$ | TDK: C1608X5R0J226M            | С              | 44   | μF   |

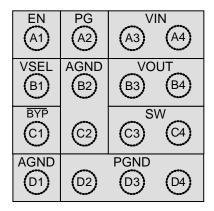

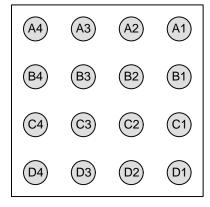

## **PIN CONFIGURATION**

Figure 3. Top Through View (Bumps Down)

Figure 4. Bottom View (Bumps Up)

## **Table 3. PIN DEFINITIONS**

| Pin #      | Name | Description                                                                                                                                                                   |

|------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1         | EN   | Enable. When this pin is HIGH, the circuit is enabled (Note 2).                                                                                                               |

| A2         | PG   | <b>Power Good</b> . This is an open–drain output. PG is actively pulled LOW if output falls out of regulation due to overload or if thermal protection threshold is exceeded. |

| A3-A4      | VIN  | Input Voltage. Connect to Li-Ion battery input power source (Note 2).                                                                                                         |

| B1         | VSEL | Output Voltage Select. When boost is running, this pin can be used to select output voltage.                                                                                  |

| B2, C2, D1 | AGND | <b>Analog Ground</b> . This is the signal ground reference for the IC. All voltage levels are measured with respect to this pin.                                              |

| B3-B4      | VOUT | Output Voltage. Place C <sub>OUT</sub> as close as possible to the device.                                                                                                    |

| C1         | ВҮР  | <b>Bypass</b> . This pin can be used to activate Forced Bypass Mode. When this pin is LOW, the bypass switches (Q3 and Q1) are turned on and the IC is otherwise inactive.    |

| C3-C4      | SW   | Switching Node. Connect to inductor.                                                                                                                                          |

| D2-D4      | PGND | <b>Power Ground</b> . This is the power return for the IC. The C <sub>OUT</sub> bypass capacitor should be returned with the shortest path possible to these pins.            |

<sup>2.</sup> The EN pin can be tied to VIN, but it is recommended to tie EN to the 1.8 V logic voltage.

**Table 4. ABSOLUTE MAXIMUM RATINGS**

| Symbol           | Parameter                                |                                      | Min. | Max.            | Unit |

|------------------|------------------------------------------|--------------------------------------|------|-----------------|------|

| V <sub>IN</sub>  | V <sub>IN</sub> Input Voltage            |                                      | -0.3 | 6.5             | V    |

| V <sub>OUT</sub> | V <sub>OUT</sub> Output Voltage          |                                      |      | 6.0             | V    |

|                  | SW Node                                  | DC                                   | -0.3 | 8.0             | V    |

|                  |                                          | Transient: 10 ns, 3 MHz              | -1.0 | 8.0             | V    |

|                  | Other Pins                               |                                      | -0.3 | 6.5<br>(Note 3) | V    |

| ESD              | Electrostatic Discharge Protection Level | Human Body Model per JESD22-A114     | 3    | .0              | kV   |

|                  |                                          | Charged Device Model per JESD22-C101 | 1    | .5              | kV   |

| TJ               | Junction Temperature                     | •                                    | -40  | +150            | °C   |

| T <sub>STG</sub> | Storage Temperature                      |                                      | -65  | +150            | °C   |

| TL               | Lead Soldering Temperature, 10 Seconds   |                                      |      | +260            | °C   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

## **Table 5. RECOMMENDED OPERATING CONDITIONS**

| Symbol          | Parameter            | Min. | Max. | Unit |

|-----------------|----------------------|------|------|------|

| V <sub>IN</sub> | Supply Voltage       | 2.35 | 5.5  | V    |

| lout            | Output Current       | 0    | 1500 | mA   |

| T <sub>A</sub>  | Ambient Temperature  | -40  | +85  | °C   |

| TJ              | Junction Temperature | -40  | +125 | °C   |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

**Table 6. THERMAL CHARACTERISTICS**

| Symbol        | Parameter                              | Тур. | Unit |

|---------------|----------------------------------------|------|------|

| $\theta_{JA}$ | Junction-to-Ambient Thermal Resistance | 80   | °C/W |

| $\theta_{JB}$ | Junction-to-Board Thermal Resistance   | 42   |      |

Junction–to–ambient thermal resistance is a function of application and board layout. This data is measured with four–layer ON Semiconductor evaluation boards (1 oz copper on all layers). Special attention must be paid not to exceed junction temperature  $T_{J(max)}$  at a given ambient temperature  $T_A$ .

<sup>3.</sup> Lesser of 6.5 V or  $V_{IN}$  + 0.3 V.

## **Table 7. ELECTRICAL CHARACTERISTICS**

Recommended operating conditions, unless otherwise noted, circuit per Figure 1,  $V_{IN} = 2.35 \text{ V}$  to  $V_{OUT}$ ,  $T_A = -40 ^{\circ}\text{C}$  to  $85 ^{\circ}\text{C}$ . Typical values are given  $V_{IN} = 3.0 \text{ V}$  and  $T_A = 25 ^{\circ}\text{C}$ .

| Symbol                | Parameter                                    | Conditi                                                                                 | on                             | Min. | Тур. | Max. | Unit |

|-----------------------|----------------------------------------------|-----------------------------------------------------------------------------------------|--------------------------------|------|------|------|------|

| ΙQ                    | V <sub>IN</sub> Quiescent Current            | Bypass Mode V <sub>OUT</sub> =                                                          | 3.5 V, V <sub>IN</sub> = 4.2 V |      | 140  | 190  | μА   |

|                       |                                              | Boost Mode V <sub>OUT</sub> = 3.                                                        | 5 V, V <sub>IN</sub> = 2.5 V   |      | 150  | 250  | μΑ   |

|                       |                                              | Shutdown: EN = 0, V <sub>IN</sub>                                                       | <sub>V</sub> = 3.0 V           |      | 1.5  | 5.0  | μΑ   |

|                       |                                              | Forced Bypass Mode<br>V <sub>IN</sub> = 3.5 V                                           | Low I <sub>Q</sub>             |      | 4    | 10   | μА   |

| I <sub>LK</sub>       | VOUT to VIN Reverse Leakage                  | V <sub>OUT</sub> = 5 V, EN = 0                                                          |                                |      | 0.2  | 1.0  | μΑ   |

| I <sub>LK_OUT</sub>   | V <sub>OUT</sub> Leakage Current             | $V_{OUT} = 0$ , $EN = 0$ , $V_{IN}$                                                     | = 4.2 V                        |      | 0.1  | 1.0  | μΑ   |

| V <sub>UVLO</sub>     | Under-Voltage Lockout                        | V <sub>IN</sub> Rising                                                                  |                                |      | 2.20 | 2.35 | V    |

| V <sub>UVLO_HYS</sub> | Under-Voltage Lockout Hysteresis             |                                                                                         |                                |      | 200  |      | mV   |

| V <sub>PG(OL)</sub>   | PG Low                                       | I <sub>PG</sub> = 5 mA                                                                  |                                |      |      | 0.4  | V    |

| I <sub>PG_LK</sub>    | PG Leakage Current                           | V <sub>PG</sub> = 5 V                                                                   |                                |      |      | 1    | μΑ   |

| V <sub>IH</sub>       | Logic Level High EN, VSEL, BYP               |                                                                                         |                                | 1.2  |      |      | V    |

| $V_{IL}$              | Logic Level Low EN, VSEL, BYP                |                                                                                         |                                |      |      | 0.4  | V    |

| R <sub>LOW</sub>      | Logic Control Pin Pull Downs<br>(LOW Active) | BYP, VSEL, EN                                                                           |                                |      | 300  |      | kΩ   |

| I <sub>PD</sub>       | Weak Current Source Pull-Down                | BYP, VSEL, EN                                                                           |                                |      | 100  |      | nA   |

| V <sub>REG</sub>      | Output Voltage Accuracy                      | Target V <sub>OUT</sub> relative to GND, DC, V <sub>OUT</sub> -V <sub>IN</sub> > 100 mV |                                | -2   |      | 4    | %    |

| $V_{TRSP}$            | Load Transient Response                      | 500–1250 mA, V <sub>IN</sub> = 3.0 V                                                    |                                |      | ±4   |      | %    |

| t <sub>ON</sub>       | On-Time                                      | V <sub>IN</sub> = 3.0 V, V <sub>OUT</sub> = 3.5 V, Load > 1 A                           |                                |      | 80   |      | ns   |

| f <sub>SW</sub>       | Switching Frequency                          | $V_{IN} = 3.0 \text{ V}, V_{OUT} = 3.9$                                                 | 5 V, Load = 1 A                | 2.0  | 2.5  | 3.0  | MHz  |

| $I_{V\_LIM}$          | Boost Valley Current Limit                   | V <sub>IN</sub> = 2.6 V                                                                 |                                | 3.3  | 3.7  | 4.1  | Α    |

| I <sub>V_LIM_SS</sub> | Boost Valley Current Limit During SS         | V <sub>IN</sub> = 2.6 V                                                                 |                                |      | 1.8  |      | Α    |

| I <sub>SS_PK</sub>    | Soft-Start Input Peak Current Limit          | LIN1                                                                                    | Fast                           |      | 900  |      | mA   |

|                       |                                              | LIN2                                                                                    | Fast                           |      | 1800 |      | mA   |

| t <sub>SS</sub>       | Soft-Start EN HIGH to Regulation             | Fast, 50 Ω Load                                                                         |                                |      | 600  |      | μS   |

| V <sub>OVP</sub>      | Output Over-Voltage Protection Threshold     |                                                                                         |                                |      | 6.0  | 6.3  | V    |

| V <sub>OVP_HYS</sub>  | Output Over–Voltage Protection<br>Hysteresis |                                                                                         |                                |      | 300  |      | mV   |

| R <sub>DS(ON)N</sub>  | N-Channel Boost Switch R <sub>DS(ON)</sub>   | V <sub>IN</sub> = 3.5 V                                                                 |                                |      | 85   | 120  | mΩ   |

| R <sub>DS(ON)P</sub>  | P-Channel Sync Rectifier R <sub>DS(ON)</sub> | V <sub>IN</sub> = 3.5 V                                                                 |                                |      | 65   | 85   | mΩ   |

| RDS(ON)P_BYP          | P-Channel Bypass Switch R <sub>DS(ON)</sub>  | V <sub>IN</sub> = 3.5 V                                                                 |                                |      | 65   | 85   | mΩ   |

| T <sub>120A</sub>     | T120 Activation Threshold                    |                                                                                         |                                |      | 120  |      | °C   |

| T <sub>120R</sub>     | T120 Release Threshold                       |                                                                                         |                                |      | 100  |      | °C   |

| T <sub>150T</sub>     | T150 Threshold                               |                                                                                         |                                |      | 150  |      | °C   |

| T <sub>150H</sub>     | T150 Hysteresis                              |                                                                                         |                                |      | 20   |      | °C   |

| t <sub>RST</sub>      | FAULT Restart Timer                          |                                                                                         |                                |      | 20   |      | ms   |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

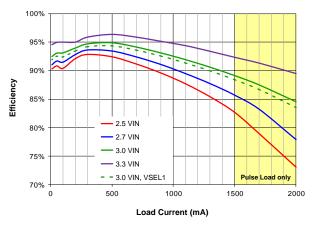

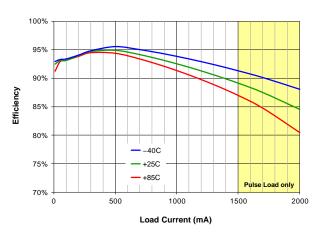

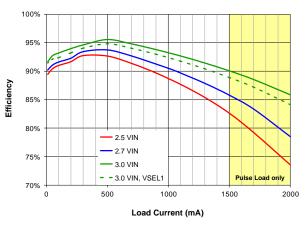

## **TYPICAL CHARACTERISTICS**

Unless otherwise specified;  $V_{IN} = 3.0 \text{ V}$ ,  $V_{OUT} = 3.5 \text{ V}$ , VSEL = 0 V, and  $T_A = 25^{\circ}C$ ; circuit and components according to Figure 1.

Figure 5. Efficiency vs. Load Current and Input Voltage

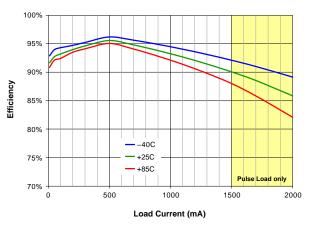

Figure 6. Efficiency vs. Load Current and Temperature

Figure 7. Efficiency vs. Load Current and Input Voltage, V<sub>OUT</sub> = 3.3 V

Figure 8. Efficiency vs. Load Current and Temperature, V<sub>OUT</sub> = 3.3 V

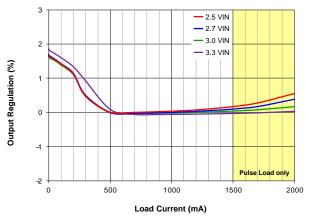

Figure 9. Output Regulation vs. Load Current and Input Voltage (Normalized to 3.0 V<sub>IN</sub>, 500 mA Load)

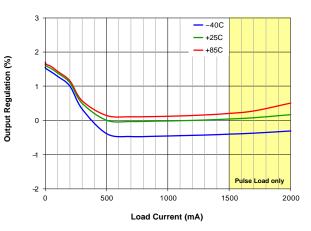

Figure 10. Output Regulation vs. Load Current and Temperature (Normalized to 3.0  $V_{IN}$ , 500 mA Load,  $T_A = 25^{\circ}C$ )

## TYPICAL CHARACTERISTICS (continued)

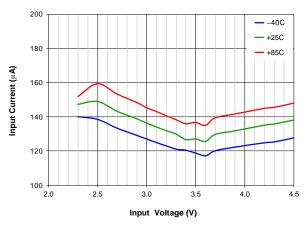

Unless otherwise specified;  $V_{IN} = 3.0 \text{ V}$ ,  $V_{OUT} = 3.5 \text{ V}$ , VSEL = 0 V, and  $T_A = 25^{\circ}\text{C}$ ; circuit and components according to Figure 1.

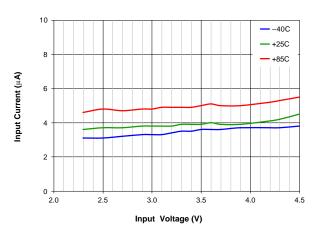

Figure 11. Quiescent Current vs. Input Voltage and Temperature, Auto Bypass

Figure 12. Quiescent Current vs. Input Voltage, Temperature, Forced Bypass (Low  $I_Q$ )

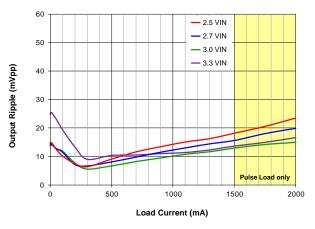

Figure 13. Output Ripple vs. Load Current and Input Voltage

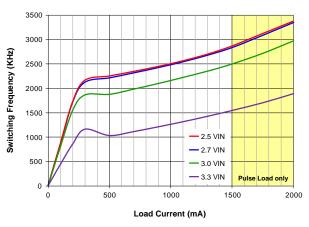

Figure 14. Switching Frequency vs. Load Current and Input Voltage

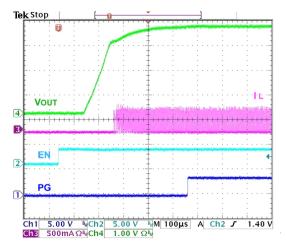

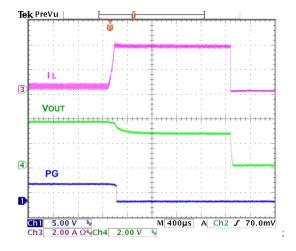

Figure 15. Startup, 50  $\Omega$  Load

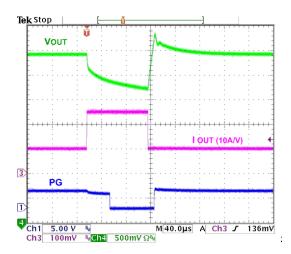

Figure 16. Overload Protection

## TYPICAL CHARACTERISTICS (continued)

Unless otherwise specified;  $V_{IN} = 3.0 \text{ V}$ ,  $V_{OUT} = 3.5 \text{ V}$ , VSEL = 0 V, and  $T_A = 25^{\circ}\text{C}$ ; circuit and components according to Figure 1.

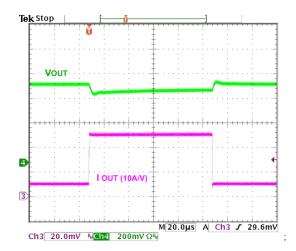

Figure 17. Load Transient, 100-500 mA, 100 ns Edge

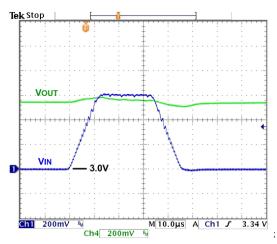

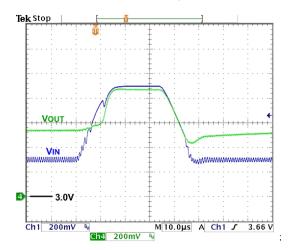

Figure 19. Line Transient, 3.0-3.6 V<sub>IN</sub>, 10 µs Edge, 1.0 A Load

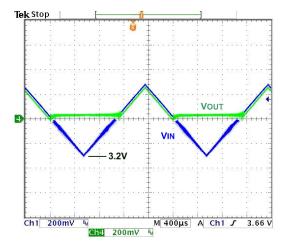

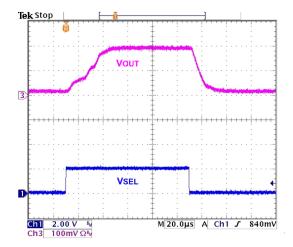

Figure 21. Bypass Entry / Exit, Slow  $V_{IN}$  Ramp 1 ms Edge, 500 mA Load, 3.2–3.8  $V_{IN}$

Figure 18. Transient Overload, 1.0–2.5 A, 100 ns Edge

Figure 20. Line Transient, 3.3–3.9  $V_{IN}, \\ 10~\mu s$  Edge, 1.0 A Load

Figure 22. V<sub>SEL</sub> Step, V<sub>IN</sub> = 3.0 V, 500 mA Load

#### **CIRCUIT DESCRIPTION**

FAN48632 is a synchronous boost regulator, typically operating at 2.5 MHz in Continuous Conduction Mode (CCM), which occurs at moderate to heavy load current and low  $V_{\rm IN}$  voltages. The regulator includes a Bypass Mode that activates when  $V_{\rm IN}$  is above the boost regulator's set point.

In anticipation of a heavy load transition, the set point can be adjusted upward by fixed amounts with the VSEL pin to reduce the required system headroom during lighter—load operation to save power.

**Table 8. OPERATING STATES**

| Mode | Description          | Invoked When                       |

|------|----------------------|------------------------------------|

| LIN  | Linear Startup       | V <sub>IN</sub> > V <sub>OUT</sub> |

| SS   | Boost Soft-Start     | $V_{OUT} < V_{OUT(MIN)}$           |

| BST  | Boost Operating Mode | $V_{OUT} = V_{OUT(MIN)}$           |

| BPS  | Bypass Mode          | $V_{IN} > V_{OUT(MIN)}$            |

#### **Boost Mode**

The FAN48632 uses a current—mode modulator to achieve excellent transient response and smooth transitions between CCM and Discontinuous Conduction Mode (DCM) operation. During CCM operation, the device maintains a switching frequency of about 2.5 MHz. In light—load operation (DCM), frequency is reduced to maintain high efficiency.

**Table 9. BOOST STARTUP SEQUENCE**

| Start<br>State | Entry                                | Exit                                          | End State | Timeout<br>(μs) |

|----------------|--------------------------------------|-----------------------------------------------|-----------|-----------------|

| LIN1           | V <sub>IN</sub> ><br>UVLO,<br>EN = 1 | V <sub>OUT</sub> ><br>V <sub>IN</sub> -300 mV | SS        |                 |

|                |                                      |                                               | LIN2      | 512             |

| LIN2           | LIN1 Exit                            | V <sub>OUT</sub> ><br>V <sub>IN</sub> -300 mV | SS        |                 |

|                |                                      | TIMEOUT                                       | FAULT     | 1024            |

| SS             | LIN1 or<br>LIN2 Exit                 | $V_{OUT} = V_{OUT(MIN)}$                      | BST       |                 |

|                |                                      | OVERLOAD<br>TIMEOUT                           | FAULT     | 64              |

## **Shutdown and Startup**

If EN is LOW, all bias circuits are off and the regulator is in Shutdown Mode. During shutdown, current flow is prevented from  $V_{IN}$  to  $V_{OUT}$ , as well as reverse flow from  $V_{OUT}$  to  $V_{IN}$ . During startup, it is recommended to keep DC current draw below 500 mA.

## LIN State

When EN is HIGH and  $V_{IN} > UVLO$ , the regulator attempts to bring  $V_{OUT}$  within 300 mV of  $V_{IN}$  using the internal fixed current source from  $V_{IN}$  (Q3). The current is limited to LIN1 set point.

If  $V_{OUT}$  reaches  $V_{IN}$ –300 mV during LIN1 Mode, the SS state is initiated. Otherwise, LIN1 times out after 512  $\mu$ s and LIN2 Mode is entered.

In LIN2 Mode, the current source is incremented to 2 A. If  $V_{OUT}$  fails to reach  $V_{IN}{-}300$  mV after 1024  $\mu s$ , a fault condition is declared.

#### SS State

Upon the successful completion of the LIN state ( $V_{OUT} \ge V_{IN}$ –300 mV), the regulator begins switching with boost pulses current limited to 50% of nominal level.

During SS state,  $V_{OUT}$  is ramped up by stepping the internal reference. If  $V_{OUT}$  fails to reach regulation during the SS ramp sequence for more than 64  $\mu$ s, a fault condition is declared. If large  $C_{OUT}$  is used, the reference is automatically stepped slower to avoid excessive input current draw.

#### BST State

This is a normal operating state of the regulator.

#### BPS State

If  $V_{IN}$  is above  $V_{REG}$  when the SS Mode successfully completes, the device transitions directly to BPS Mode.

Table 10. EN AND BYP LOGIC TABLE

| EN | BYP | Mode          | V <sub>OUT</sub>                               |

|----|-----|---------------|------------------------------------------------|

| 0  | 0   | Shutdown      | 0                                              |

|    | 1   | Shutdown      | 0                                              |

| 1  | 0   | Forced Bypass | V <sub>IN</sub>                                |

|    | 1   | Auto Bypass   | $V_{REG}$ or $V_{IN}$ (if $V_{IN} > V_{REG}$ ) |

#### **FAULT State**

The regulator enters the FAULT state under any of the following conditions:

- V<sub>OUT</sub> fails to achieve the voltage required to advance from LIN state to SS state.

- V<sub>OUT</sub> fails to achieve the voltage required to advance from SS state to BST state.

- Boost current limit triggers for 2 ms during the BST state.

- V<sub>DS</sub> protection threshold is exceeded during BPS state.

Once a fault is triggered, the regulator stops switching and presents a high-impedance path between  $V_{\rm IN}$  and  $V_{\rm OUT}$ . After waiting 20 ms, a restart is attempted.

## **Power Good**

Power good is 0 FAULT, 1 POWER GOOD, open-drain input.

The Power good pin is provided for signaling the system when the regulator has successfully completed soft—start and no faults have occurred. Power good also functions as an early warning flag for high die temperature and overload conditions.

- PG is released HIGH when the soft-start sequence is successfully completed.

- PG is pulled LOW when PMOS current limit has triggered for 64 μs OR the die the temperature exceeds 120°C. PG is re–asserted when the device cools below to 100°C.

- Any FAULT condition causes PG to be de-asserted.

#### Over-Temperature

The regulator shuts down when the die temperature exceeds 150°C. Restart occurs when the IC has cooled by approximately 20°C.

## **Bypass Operation**

In normal operation, the device automatically transitions from Boost Mode to Bypass Mode, if  $V_{IN}$  goes above target  $V_{OUT}.$  In Bypass Mode, the device fully enhances both Q1 and Q3 to provide a very low impedance path from  $V_{IN}$  to  $V_{OUT}.$  Entry to the Bypass Mode is triggered by condition where  $V_{IN} > V_{OUT}$  and no switching has occurred during past 5  $\mu s.$  To soften the entry to Bypass Mode, Q3 is driven as a linear current source for the first 5  $\mu s.$  Bypass Mode exit is triggered when  $V_{OUT}$  reaches the target  $V_{OUT}$  voltage. During Automatic Bypass Mode, the device is short—circuit protected by voltage comparator tracking the voltage drop from  $V_{IN}$  to  $V_{OUT}$ ; if the drop exceeds 200 mV, FAULT is declared.

With sufficient load to enforce CCM operation, the Bypass Mode to Boost Mode transition occurs at the target  $V_{OUT}$ . The corresponding input voltage at the transition point is:

$$V_{\text{IN}} \le V_{\text{OUT}} + I_{\text{LOAD}} \cdot (\text{DCR}_{\text{L}} + R_{\text{DS(ON)P}}) \| R_{\text{DS(ON)BYP}}$$

(eq. 1)

The Bypass Mode entry threshold has 25 mV hysteresis imposed at VOUT to prevent cycling between modes. The transition from Boost Mode to Bypass Mode occurs at the target  $V_{OUT}$  + 25 mV. The corresponding input voltage is:

$$V_{IN} \ge V_{OUT} + 25mV + I_{LOAD} \cdot (DCR_L + R_{DS(ON)P})$$

(eq. 2)

#### **Forced Bypass**

Entry to Forced Bypass Mode initiates with a current limit on Q3 and then proceeds to a true bypass state. To prevent reverse current to the battery, the device waits until output discharges below  $V_{\rm IN}$  before entering Forced Bypass Mode.

Low-I<sub>Q</sub> Forced Bypass Mode is available for the FAN48632. After the transition is complete, most of the internal circuitry is disabled to minimize quiescent current draw. OCP, UVLO, output OVP and over-temperature protections are inactive in Forced Bypass Mode.

In Forced Bypass Mode,  $V_{OUT}$  can follow  $V_{IN}$  below  $V_{OUT(MIN)}$ .

## **VSEL**

$V_{SEL}$  can be asserted in anticipation of a positive load transient. Raising  $V_{SEL}$  increases  $V_{OUT(MIN)}$  by a fixed amount and  $V_{OUT}$  is stepped to the corresponding target output voltage in 20  $\mu s$ . The functionality can also be utilized to mitigate undershoot during severe line transients, while minimizing  $V_{OUT}$  during more benign operating conditions to save power.

## **APPLICATION INFORMATION**

## Output Capacitance (COUT)

Stability

The effective capacitance ( $C_{EFF}$ ) of small, high–value, ceramic capacitors decreases as bias voltage increases. FAN48632 is guaranteed for stable operation with the minimum value of  $C_{EFF}$  ( $C_{EFF(MIN)}$ ) of 14  $\mu$ F.

## Inductor Selection

The recommended nominal inductance value is  $0.47~\mu H$ . FAN48632 employs valley–current limiting; peak inductor current can exceed 4.4 A for a short duration during overload conditions. Saturation effects cause the inductor current ripple to become higher under high loading as only valley of the inductor current ripple is controlled.

#### Startup

Input current limiting is in effect during soft–start, which limits the current available to charge  $C_{OUT}$  and any additional capacitance on the  $V_{OUT}$  line. If the output fails to achieve regulation within the limits described in the Startup section, a FAULT occurs, causing the circuit to shut down then restart after a significant time period. If the total combined output capacitance is very high, the circuit may not start on the first attempt, but eventually achieves regulation if no load is present. If a high–current load and high capacitance are both present during soft–start, the circuit may fail to achieve regulation and continually attempts soft–start, only to have the output capacitance discharged by the load when in a FAULT state.

#### Output Voltage Ripple

Output voltage ripple is inversely proportional to  $C_{OUT}$ . During  $t_{ON}$ , when the boost switch is on, all load current is supplied by  $C_{OUT}$ . Output ripple is calculated as:

$$V_{RIPPLE(P-P)} = t_{ON} \cdot \frac{I_{LOAD}}{C_{OUT}}$$

(eq. 3)

and

$$t_{ON} = t_{SW} \cdot D = t_{SW} \cdot \left(1 - \frac{V_{IN}}{V_{OUT}}\right)$$

(eq. 4)

therefore:

$$V_{RIPPLE(P-P)} = t_{SW} \cdot \left(1 - \frac{V_{IN}}{V_{OUT}}\right) \cdot \frac{I_{LOAD}}{C_{OUT}}$$

(eq. 5)

and

$$t_{SW} = \frac{1}{f_{SW}}$$

(eq. 6)

As can be seen from eq. 5, the maximum  $V_{RIPPLE}$  occurs when  $V_{IN}$  is at minimum and  $I_{LOAD}$  is at maximum.

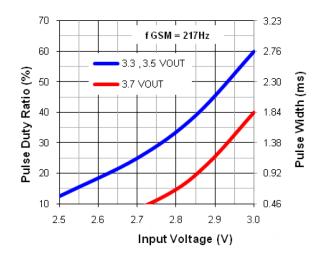

## 2.0 A Pulsed Loads for GSM Applications

The FAN48632 can support 2 A load pulses for GSM and GSM Edge applications, according to the minimum  $V_{\rm IN}$  levels shown in Figure 23.

Figure 23. Minimum V<sub>IN</sub> for 2 A GSM Pulse, 3.5 V<sub>OUT</sub>

Results shown use circuit/components of Figure 1 with device mounted on standard evaluation platform (layout Figure 24).

## **Layout Recommendation**

To minimize spikes at  $V_{OUT}$ ,  $C_{OUT}$  must be placed as close as possible to PGND and VOUT, as shown in Figure 24. The associated PGND and  $V_{OUT}$  routes are best made directly on the top copper layer, rather than thru vias.

For thermal reasons, it is suggested to maximize the pour area for all planes other than SW. Especially the ground pour should be set to fill all available PCB surface area and tied to internal layers with a cluster of thermal vias.

Figure 24. Layout Recommendation

## Table 11. PRODUCT-SPECIFIC DIMENSIONS

| D            | E            | Х     | Υ     |

|--------------|--------------|-------|-------|

| 1.780 ±0.030 | 1.780 ±0.030 | 0.290 | 0.290 |

TINYBOOST is registered trademark of Semiconductor Components Industries, LLC (SCILLC) or its subsidiaries in the United States and/or other countries.

## WLCSP16 1.78x1.78x0.586 CASE 567SY ISSUE O

**DATE 30 NOV 2016**

RECOMMENDED LAND PATTERN (NSMD PAD TYPE)

## **NOTES**

- A. NO JEDEC REGISTRATION APPLIES.

- B. DIMENSIONS ARE IN MILLIMETERS.

- C. DIMENSIONS AND TOLERANCE PER ASME Y14.5M, 1994.

- DATUM C IS DEFINED BY THE SPHERICAL CROWNS OF THE BALLS.

- E. PACKAGE NOMINAL HEIGHT IS

586 ± 39 MICRONS (547-625 MICRONS).

FOR DIMENSIONS D,E,X, AND Y SEE

PRODUCT DATASHEET.

| DOCUMENT NUMBER: | 98AON16621G             | Electronic versions are uncontrolled except when accessed directly from the Document Repos<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |

|------------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| DESCRIPTION:     | WLCSP16 1.78x1.78x0.586 |                                                                                                                                                                               | PAGE 1 OF 1 |

ON Semiconductor and are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights of others.

onsemi, ONSEMI, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does **onsemi** assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using **onsemi** products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by **onsemi**. "Typical" parameters which may be provided in **onsemi** data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. **onsemi** does not convey any license under any of its intellectual property rights nor the rights of others. **onsemi** products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use **onsemi** products for any such unintended or unauthorized application, Buyer shall indemnify and hold **onsemi** and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that **onsemi** was negligent regarding the design or manufacture of the part. **onsemi** is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### PUBLICATION ORDERING INFORMATION

LITERATURE FULFILLMENT: Email Requests to: orderlit@onsemi.com

onsemi Website: www.onsemi.com

**TECHNICAL SUPPORT** North American Technical Support: Voice Mail: 1 800–282–9855 Toll Free USA/Canada

Phone: 011 421 33 790 2910

Europe, Middle East and Africa Technical Support:

Phone: 00421 33 790 2910

For additional information, please contact your local Sales Representative